中国科学技术大学

2017-2018 学年第 一 学期考试试卷

考试科目: 数字逻辑电路 得分: \_\_\_\_\_

学生所在院系: \_\_\_\_\_ 姓名: \_\_\_\_\_ 学号: \_\_\_\_\_

一、简答题 (每题 8 分, 共 40 分)

1. 用卡诺图求逻辑函数  $Y(A, B, C, D) = \sum m(2, 3, 4, 5, 6, 7, 12, 13) + d(10, 14, 15)$  的最简与或式和最简与或非式。

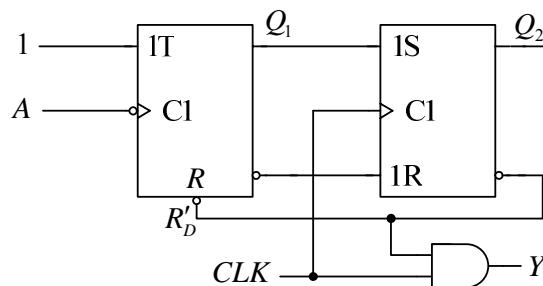

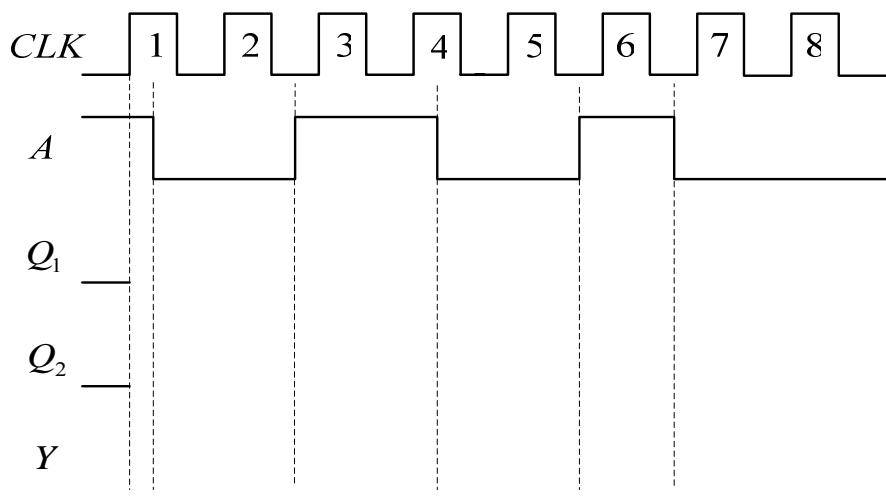

2. 电路如图 1-1(a)所示。试对应图 1-1(b)所示时钟信号  $CLK$  和输入  $A$  的波形, 画出  $Q_1$ 、 $Q_2$  和输出  $Y$  的波形, 设触发器的初始状态均为 0。

图 1-1 (a)

图 1-1 (b)

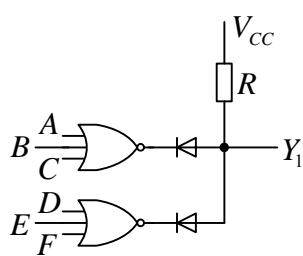

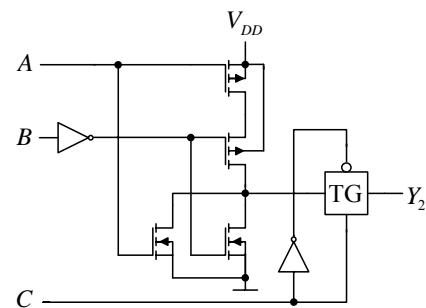

3. 图 1-2 中门电路均为 CMOS 逻辑门, 分别写出输出  $Y_1$  和  $Y_2$  的逻辑函数式。

图 1-2 (a)

图 1-2 (b)

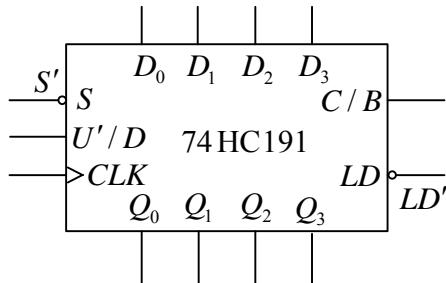

4. 74HC191 是同步十六进制加/减计数器, 将 74HC191 设计成十二进制减法计数器, 标出借位输出端。74HC191 的功能表和框图见表 1-1 和图 1-3。

| $CLK$      | $S'$     | $LD'$ | $U'/D$   | 工作状态     |

|------------|----------|-------|----------|----------|

| $\times$   | 1        | 1     | $\times$ | 保持       |

| $\times$   | $\times$ | 0     | $\times$ | 预置数 (异步) |

| $\uparrow$ | 0        | 1     | 0        | 加法计数     |

| $\uparrow$ | 0        | 1     | 1        | 减法计数     |

表 1-1

图 1-3

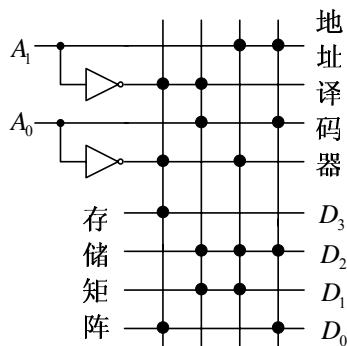

5. 图 1-4 是某 PROM 电路编程后的点阵图。(1) 列出数据表; (2) 若把地址  $A_1, A_0$  看作输入, 数据  $D_3, D_2, D_1, D_0$  作为输出, 分别写出  $D_3, D_2, D_1, D_0$  的表达式。

图 1-4

## 二、组合电路分析与设计 (每题 10 分, 共 20 分)

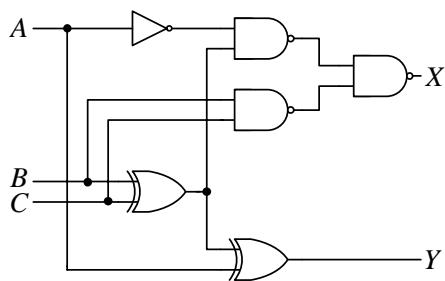

1. 电路如图 2-1 所示, (1) 写出输出的逻辑函数式; (2) 列出真值表, 说明电路的逻辑功能。

图 2-1

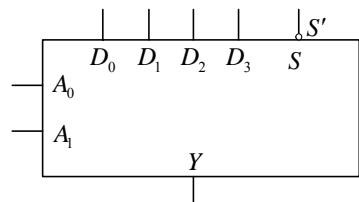

2. 用 4 选 1 数据选择器设计一个组合电路。输入  $ABC$  为 3 位二进制数, 当输入能被 3 整除时输出  $Z=1$ , 否则  $Z=0$ 。数据选择器的功能表和框图见表 2-1 和图 2-2。

(注: 0 可被任何数整除)

| $S'$ | $A_1$    | $A_0$    | $Y$   |

|------|----------|----------|-------|

| 1    | $\times$ | $\times$ | 0     |

| 0    | 0        | 0        | $D_0$ |

| 0    | 0        | 1        | $D_1$ |

| 0    | 1        | 0        | $D_2$ |

| 0    | 1        | 1        | $D_3$ |

表 2-1

图 2-2

### 三、时序电路分析与设计（每题 15 分，共 30 分）

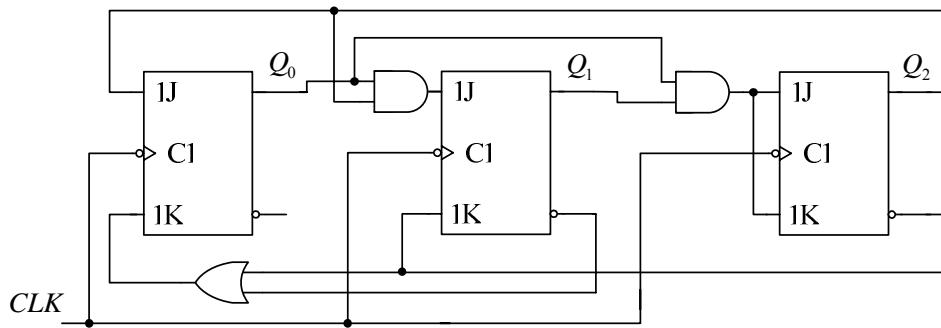

1. 分析图 3-1 所示时序逻辑电路，写出电路的驱动方程和状态方程，列出状态转换表，画出状态转换图，检查电路能否自启动，说明电路的功能。

图 3-1

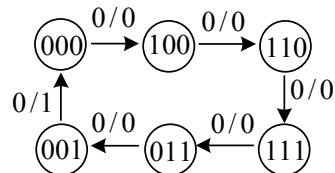

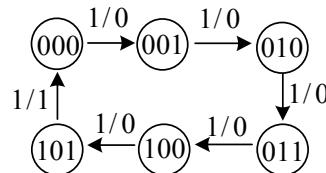

2. 用上升沿触发的  $D$  触发器和门电路设计一个可控计数器,  $A$  是控制端,  $Y$  是输出端。当  $A=0$  时状态转换图如图 3-2(a) 所示, 当  $A=1$  时状态转换图如图 3-2(b) 所示。

(1) 求电路的状态方程、输出方程和驱动方程; (2) 画出逻辑图。

图 3-2(a)

图 3-2(b)

装订线 答题时不要超过此线

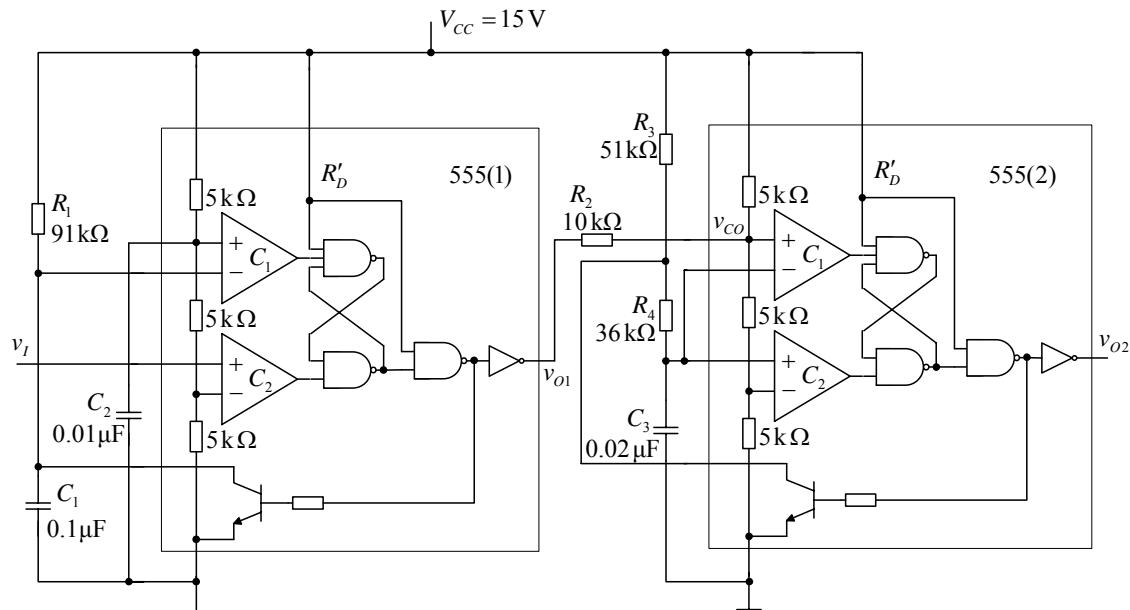

#### 四、脉冲电路分析 (10 分)

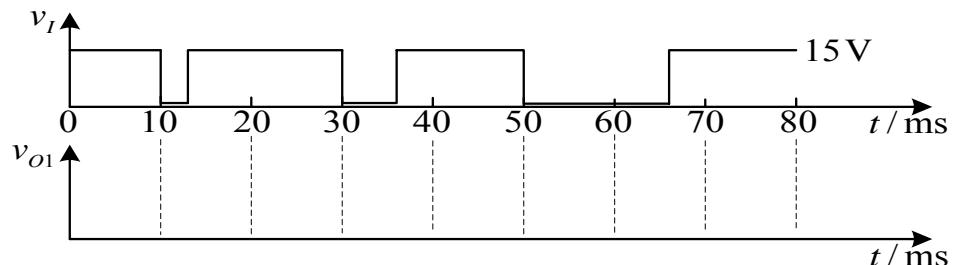

电路如图 4-1(a)所示, (1) 已知 $v_I$ 的波形如图 4-1(b) 所示, 求 $v_{o1}$ 输出脉冲的宽度并画出 $v_{o1}$ 的波形; (2) 若 555 定时器输出的高电平为 14V, 输出电阻可忽略不计, 求 $v_{o1}$ 为高电平时 $v_{o2}$ 输出波形的周期。

图 4-1(a)

图 4-1(b)