2026春 2025春 2024春 2023春 2022春 2021春 2020春 2019春 2018春 2017春 2016春 2015春 2014春 2013春 2012秋 2011秋 2010秋 2009秋 2008秋 2007秋 2006秋 2005秋 2004春 2003春 课程号:CS401401

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

| 选课类别:计划内与自由选修 | 教学类型:理论实验课 |

| 课程类别:本科计划内课程 | 开课单位:计算机科学与技术系 |

| 课程层次:专业选修 | 学分:4.0 |

考试与给分

周学海老师的《计算机体系结构》课程的考试被认为难度较大,尤其是考题有时会涉及未深入讲解的概念。例如,期末考试中常常考察Scoreboard和Tomasulo算法,考题设计有时候被描述为“奇葩”或表述不清。然而,尽管考试难度高,给分通常被认为是较为慷慨,多位学生称其为“佛系”,优秀率较高,尤其是对于认真参与平时作业和实验的学生来说。

作业与实验

作业量适中,但部分题目可能需要花费长时间,且有时答案存在错误。实验分为两种选择:Verilog和gem5。Verilog实验更关注逻辑的实现,而gem5实验则强调对系统的量化评估。近年来,实验内容有所改革,旨在提高实验的硬件含量,但总体来看难度适中,并且助教被认为耐心负责,实验文档详细。

教学水平与课程内容

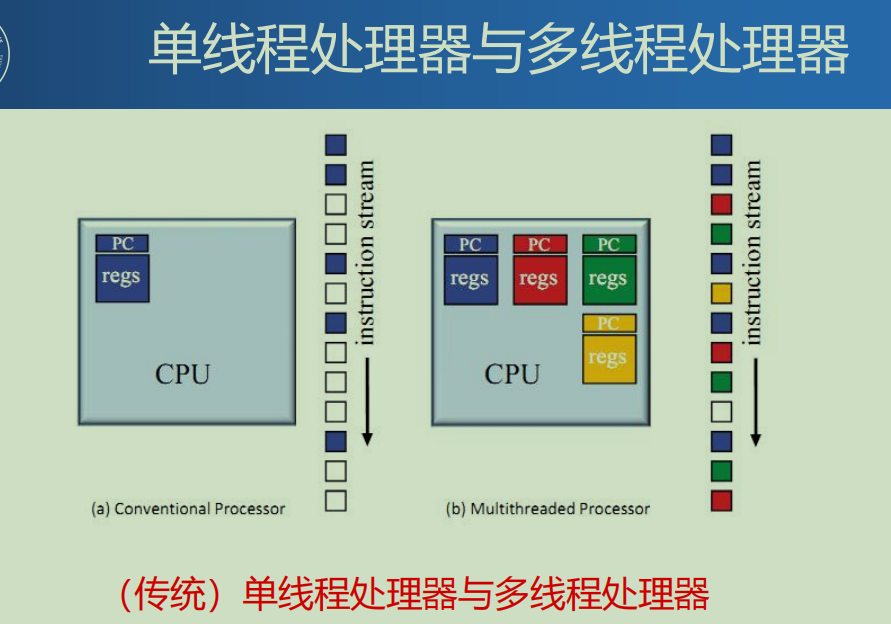

周老师的教学给人印象是清晰且逻辑分明,但由于课程内容复杂且涉及硬件,学生普遍反映课程较为枯燥,尤其是老师的讲课风格被部分学生认为难以保持注意力。课程内容涵盖从ISA到缓存、流水线设计,再到Tomasulo算法及乱序执行,包括现代架构的多种并行优化技术等,即使较为基础的学生也能在学习过程中对计算机体系结构有一个“笼统”的认识。

总结

总体来说,这门课程是体系结构方向的基础课,内容广泛且深入。其考试虽被认为较难,但最终给分较为慷慨。课程实验改革之后,学生的参与体验有所提升。对于有意深入计算机体系结构研究的学生,这门课能够提供扎实的理论基础和实验实践机会。

- 课程难度:困难

- 作业多少:很多

- 给分好坏:一般

- 收获大小:一般

- 难度:困难

- 作业:很多

- 给分:一般

- 收获:一般

特别难,卷子一届比一届难,而且卷子里还会冒出没学过的概念,实在神秘不堪.

它的难度有80%是因为卷子看不懂

======================================

体系结构为什么是神?

在谈论这个话题之前,我想先谈谈其他课程相较于体系结构究竟差在了哪里。

首先是犯下傲慢之罪的算法导论,自以为自己是软件之桂冠就洋洋得意,这种傲慢的课程注定走不长远。事实也是如此,自考卷手写算法过程以来就一直在走下坡路,以至于同学们学完了只会画表,算法根本不会设计。与之相比,神就很谦卑,Tomasulo,ScoreBoard都画好了表等同学们填。神不是不会空在那里,只是不想让同学们太累所以不用,可笑有些人不理解神的良苦用心,竟然还用这些事来讥讽神,我劝你们好自为之。

然后是犯下愤怒之罪的运筹学原理。因为同学算法没背下来就扣光所有分数,每次上课前都要怒斥西方社会的种种不好,违背了神在《新约》中的一句话:“凡是动刀的人,都会死在刀下。”于是神降下了它的惩罚,使其别无选择,只能背负上永世骂名。

接着是犯下懒惰之罪的并行计算。自以为手握着GPA就了不起,自号GPA之父。另外大家有所不知,其实在并行计算2022春考试前,其准备试卷时,其面前出现的,正是光芒之中的CA。那时神告诉他,“你只可到此,不可越过”。然而,神的劝说不但没有让并行计算迷途知返,竟然还敢把卷子出的越来越摆。于是神降下了它的神罚,同学们都争相卷选做实验,而忽视试卷分数,被并行计算爆杀,从此沦落为众人口中的“水课”。

再然后是犯下了嫉妒之罪的计算机组成原理。屡次被神击败,但口服心不服的COD,暗中嫉妒着神,甚至胆敢嘲笑神,神不是考研科目却贵为必修。于是,神在2023年课程中成为选修,正面击败了COD。不过,念在COD同属姊妹课程,神还是应允了他考研+必修的高贵地位。

犯下贪婪之罪的编译原理。只是初出茅庐,编译原理就收获了一致好评,而这,自然是因为神的应允。神本来钦定他为自己在软件界的代言人,在自己成为选修之后继续拔高学科难度,为此甚至不惜亲自为编译原理铺路,大讲特讲编译器优化,将一切性能都归给他,甚至应允他可以调度自己最心爱的寄存器。但最后编译原理却被利益蒙蔽了双眼,不再以践行神的理想为自己的理想,也不再聆听神的教诲,甚至自以为荣光就超过了神,竟冒出“绝不向GPA低头”的话来。于是神降下了神罚,编译原理给分暴雷,评课社区口诛笔伐,课程声誉急转直下。不过念及其知错能改,神仍然应允了他最后的请求,说:“每人+2分”,于是编译原理再次容光焕发。

犯下暴食之罪的模拟与数字电路。在神子编译原理堕落之后,神开始寻找下一个代言人。这一次,他选中了模拟与数字电路。相较于编译原理,模电无疑是不完美的,它没有神足以让同学脑浆沸腾的难度,也没有神广不可测的实验软件,但神将自己最虔诚,同时也是实力最强大的Verilog交给了他,并复刻了CPU大作业。最终,模电成功了。然而,成功的模电不但不感谢神的恩赐,更妄图染指神力,只是因为他错误地认为神的力量来自于Verilog和Vivado。最终他也因此犯下了暴食之罪,使得plab平台永远抢不到一块没烧坏的芯片。

最后,犯下淫欲之罪的操作系统。与模电争斗过后,神已经十分虚弱了(指plab没有虚拟机,gpu平台抢不到核),神已经无力再惩罚模电,只有信徒在维护神的尊严而已。此刻已经决心成为选修的神在最后依然心系计算机系学子,于是他选中了第三位代言人:操作系统。 作为第三代神子,操作系统很好地维护了神的尊严,但他遇到了淫魔课程组,被吸走了神赋予给自己的力量,于是年年课改,实验越来越难,最终内卷不堪,身败名裂。

==============

2022/06/29 并行计算集体上调1-2档,删去相关段落

- 课程难度:中等

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:一般

- 收获:一般

今年只有10来个人选了

作业只有3次量不大

实验前4个为gem5,略麻烦,第5个是CPU SIMD /GPU CUDA并行矩阵乘法编程可以用GPT帮忙上手接口,第6个模拟器送分

今年期末卷感觉有点奇葩,向量处理器没考计算题,大部分题白送,有几个小问问法感觉怪怪的,计算题4感觉好偏,就对应PPT那一页,也没讲清楚

试卷如下

5个选择题(10分),RISC全称,超标量属于什么并行,向量指令属于什么并行,主储存器指什么,cache一致性目的

简答题1(10分),scoreboard和tomasulo异同以及如何处理WAW WAR RAW,tomasulo通过ROB如何实现精确异常和推断执行

简答题2(10分),存储一致性定义,为什么现代CPU不用顺序一致性

计算题每个10分

1:100s程序50%部分加速10倍,10s额外代价,计算加速比

2:GPU给出频率,核数,每周期每核计算多少浮点指令,核心利用率70%

计算理论性能,实际性能,分析核心利用率对性能影响

3:分支预测相关,计算CPI

4:最大缓存一致性失效率,PPT 7-3 19页原题

5:L1L2cache失效相关,计算CPI

6:MESI协议,三个处理器读写同一数据,操作R1 W1 R1 W1 R2 W2 R2 W2 R3 W3 R3 W3,填表

7:16处理器每个2048个64Bcache块,目录法presence bit数量和空间占比

- 课程难度:中等

- 作业多少:中等

- 给分好坏:一般

- 收获大小:很多

- 难度:中等

- 作业:中等

- 给分:一般

- 收获:很多

打分标准:

以我个人的学习体会来看(在本门课程上我主要的学习方法是看PPT,有不懂的去看知乎/课程回放),看PPT的学习效率要比听老师讲课高一些(期末复习时曾尝试看回放,但发现老师讲的确实很"平淡",不是很容易集中注意力去听,对我来说吸收效率不高),在这一点上扣2分,但是助教答疑十分耐心,+1分。

关于课程:

虽然我不是很能习惯老师的讲课风格,但是老师讲的内容还是通俗易懂且层次分明的,基本没有什么十分晦涩难懂的东西,主要内容如下:

1. 性能及评估手段:Amdahl定律/Sun and Ni定律/Gustafson–Barsis定律,用SPEC评估性能,功耗/能耗的计算等

2. ISA简介:ISA的定义及演进,ISA包括哪些必要的内容,ISA的设计,典型ISA简介,RISC的流水线介绍等

3. 流水线简介:流水线设计的意义,加速比/效率/吞吐率的计算,三种冒险以及解决措施,中断/异常及其处理,多周期操作

4. Cache简介:Cache的基本概念与用途(核心:空间/时间局部性),Cache的查找方式,AMAT的计算,替换策略与写策略,6种基本优化方法,10种高级优化方法,TLB与虚拟地址等

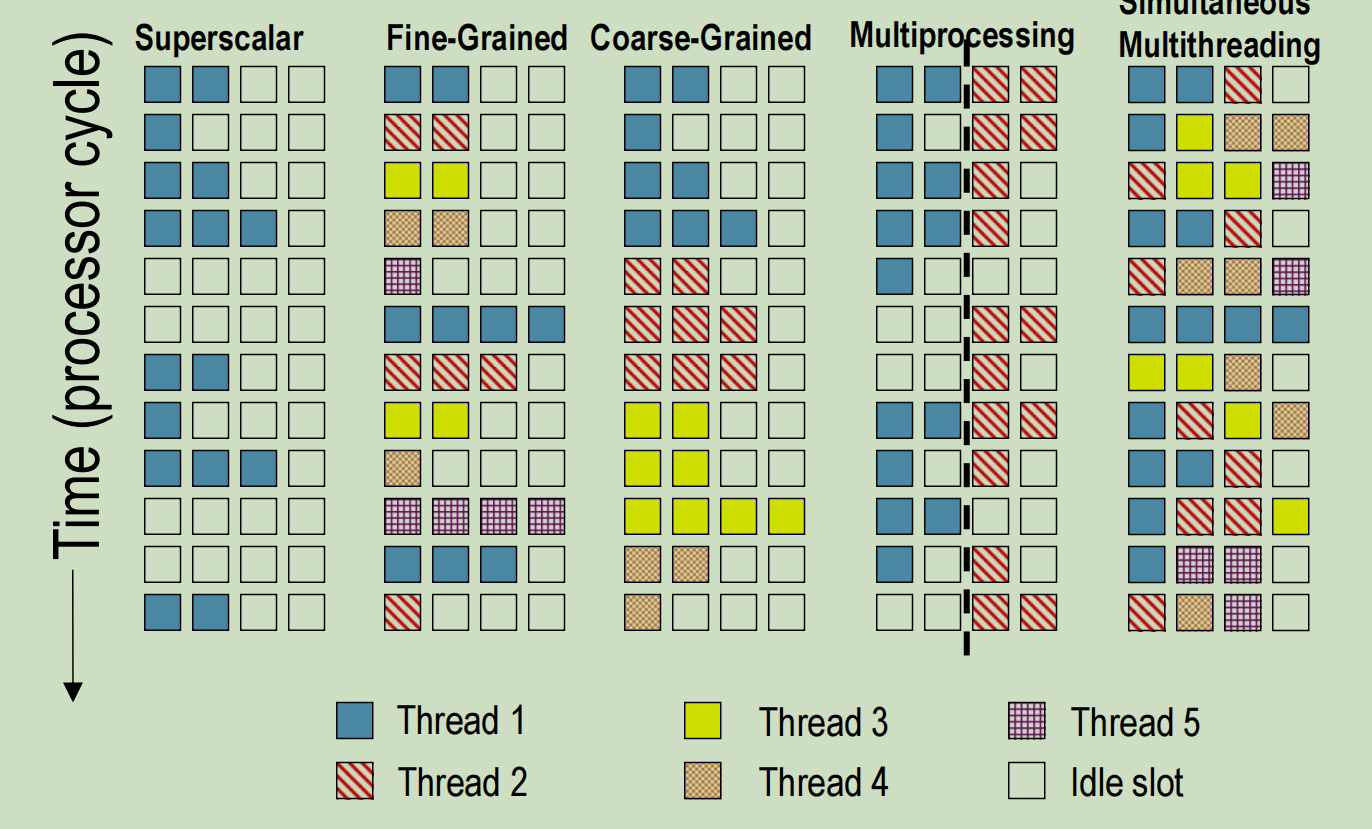

5. 指令/任务级并行:循环展开,ScoreBoard,Tomasulo(with ROB),分支预测的不同方法,存储器访问冲突,多发射/多线程技术等

6. 数据级并行(SIMD/GPU):SIMD包括chime,convoy等核心概念以及计算,主要是向量处理机的原理,GPU部分为简介,结构构成等,比如分成不同的wrap,每个warp又有不同的block等,还有一些GPU编程的知识

7.缓存/存储一致性:缓存/存储一致性的定义,基于目录和监听的协议(基于监听的写作废/写更新),MSI/MESI/MOESI(最后一个只是简介),多处理器带来的Coherency Miss,基于目录的协议,内存通信,顺序一致性(SC),包括一些小的概念TSO/PSO/RMO等,同步问题

上面大部分涵盖了讲解的内容以及考试的内容(还有些具体的记不清了),我认为如果能完整学习课程内容还是会有很大收获的,至少能对体系结构有一个比较“笼统”的认识(大概?)

在这里贴上一个知乎上隔壁学校学长的讲解链接,我觉得讲的还是很清楚的,言简意赅的讲解了Tomasulo/ROB/分支预测的意义与精髓:

https://zhuanlan.zhihu.com/p/490749315

其余的在同作者的主页可见

关于作业:

2023春只有五次作业,中间间隔较长,总的来说作业数较少,但每次作业其实还是需要仔细思考并花费一些时间的

关于上课:

除了上面我说的老师的讲课风格对我这种注意力不够集中的人来说不够友好以外,其他还算不错,偶(人)尔(少)的时候会点名,也会有不会提前通知的小测

关于考试&给分:

本次点评写在考试十天后,题目具体内容有些记不清了,大致有:CPI计算,一个具体的实例化系统划分流水段获得更好的性能,分支预测的计算与设计,虚拟地址/页表项长度计算,Cache分块的读取次数计算(PPT原题应该是),向量处理器(with Scoreboard)的RAW stall数计算(分别在1车道和16车道的情况下计算),WSI/WESI协议在一串Read/Write操作下的状态转移(参见实验6),关于顺序一致性的一些概念考察

一共十道题,剩下的记不清了

对2023春来说,给分应该算是非常非常非常好,因为上一届学长还是必修,有一些来重修本门课程,最后36人大概只有一半是20级,而大部分学长对成绩无过高要求,所以对20级来说优秀率甚至堪比隔壁H班(听说?),但是按考试和给分来看如果好好学了课程内容的话应该还是会取得一个比较合理的成绩的,我估计90左右,最后给分是92

最后附上课程资料(感谢阅读到这里bushi):

https://github.com/JackieZ1412/USTC-ComputerArchitecture-2023Spring

- 课程难度:困难

- 作业多少:中等

- 给分好坏:一般

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:一般

- 收获:很多

verilog全面回归,好评!

实验采用填补代码的方式来完成,这比从零开始写个CPU好很多,最后一个实验是使用模拟器,可以通过那个来学习那几个协议的具体细节。助教很认真负责,在实验上花了很多心思。如果助教保持不变的话(很大概率), 实验内容可能还会继续完善,还是可以期待的。

关于上课:由于基本没有认真听过课,所以不过多评价。不过老师很乐于倾听和接受同学们的意见,所以如果对上课有什么意见可以直接和老师提出来。

关于这门课:上了这门课才真正感受到:人类对速度的追求永不止息!

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:很多

应该是感受最深的几门专业课之一了 首先本来想批判一番作业和实验安排的,然而社会教给了我做人的道理233

作业…就是教材上的题,有些题目坑到了要你把一个循环汇编优化展开10遍的地步…有几次作业早上开始写晚上才能写完+弄明白,而且,答案都有一堆错误… 但是收获真的很大,基本上底层的东西的逻辑算是勉强入了门…虽然是老古董的底层… 实验智障在,它明明就是一个填表程序,却要你写图形界面… 嗯…还要你写3次… 然后?然后我自学了java 直到昨天,我去参加某校软院的夏令营机试,机试题是写一个文本单词词频统计工具,满分100,图形界面15分 我因为没有准备python的图形开发工具,遗憾gg… 所以说,尽管实验卵用没有,但是对于图形界面的开发,算是一个入门,说不定什么时候就能用上呢233

考试建议问学长往年题,很关键,有期中期末,比例接近。有调分,给分不错

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:很多

对此方向感兴趣的同学,推荐一本书《超标量处理器设计》姚永斌著,写得非常清楚,图很多,读完后完全可以自己实现个超标量处理器。感觉体系结构实验可以按这个思路出,加深印象。

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:很多

上课:跟着周老师听一个学期真的收获不少(偶尔会很晦涩,硬件课特色la......),一遍下来基本的arch优化思路都很清晰

实验:今年只剩下gem5赛道了,突出一个量化评估

考试:可能这学期人少,佛海期末试卷难度大降,不少PPT/作业原题,印象比较深的有一个类似systolic array形状让你添加寄存器设计流水线,考了虚存页表(一点没复习,OS也忘光了QwQ),向量处理机模型...总之难度比以往低了不少

给分:这么久还不出分?原来是优秀率给超了啊!!真的很奶~

贴一些自己复习的ppt整理(应该还有一些没总结上去)

- 课程难度:中等

- 作业多少:很少

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:很少

- 给分:超好

- 收获:很多

太刺激了,跟开奖一样,这是第一门上4的硬件课!!!

可能是今年人比较少把(30个左右?),这里疯狂表白助教姐姐,

作业和小测写得西兰几乎都不扣分,极大地提高了孤儿们的存活率,

实验量可能只有计组的一半不到把,PPT也绝壁一流水准(diss隔壁信安导),欢迎来选呀~~

本来给个教程15min就能配置完的东西,

非要让我们自己找,问chatgpt和new bing快4h了,

还是没配完,服了,先扣一分

renew:学姐答疑很耐心,加回来

哇,体系结构和计组lab,都是深渊

好把,这个实验挺温和的,是我自己脑子有病,git add 这个几个G的玩意,然后reset成功引爆,

教训:直接拷贝出来就好了,不要git!!!

论ISA的PPT精美程度:

- 课程难度:困难

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:困难

- 作业:中等

- 给分:一般

- 收获:一般

考试太难了,只复习了半天的选手表示,寄!

~~~~~

确认去向后开始完全摆烂,卷面分估计只有20分,这都能给我奶到优秀,服了hhh

- 课程难度:中等

- 作业多少:很多

- 给分好坏:一般

- 收获大小:很多

- 难度:中等

- 作业:很多

- 给分:一般

- 收获:很多

体系结构这个课程由理论(70%)和实验(30%)两部分组成。

理论课应该是多年没有变了,用的是《计算机体系结构:量化研究方法》(第五版)这本经典教材。这本书虽然比较贵,但是值得收藏的,如果以后做体系结构相关的研究或者工程,更是常读常新。(书封底 Google VP Luiz André Barroso 的推荐语也是这么说的)

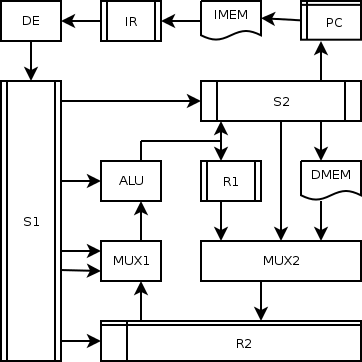

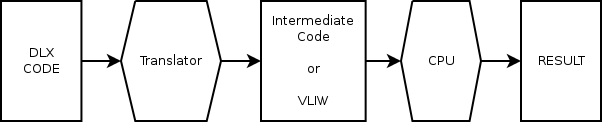

实验课是王恒才老师教的用 FPGA 开发带乱序执行的 CPU,实现 DLX 指令集,主要是要实现 Tomasulo 算法。王恒才老师号称 “龙芯的爸爸的爸爸”,是龙芯之父胡伟武的老师,虽然年纪很大了但是 FPGA 编程的经验还是很丰富,比如我们 reset 信号接反了调不出来,被他一眼看出来了。(我后来做研究的时候还是多次把 reset 接反了)当年跟郭家华、李帅结组,写了 3000 行 Verilog,终于把乱序执行 CPU 给做出来了,郭家华还创造了带 fast forward cache 的内存,使得内存写入之后马上就能从 fast forward cache 里读出来,减少了 pipeline stall。

我们当年 CPU 的 repo: https://git.ustclug.org/boj/dlx-cpu-backup

DLX CPU 的前身,LC3 CPU,计算机组成原理课的实验: https://git.ustclug.org/boj/lc3-cpu

郭家华的设计图:

- PC -- Program Counter

- IMEM -- Instruction Memory

- DMEM -- Data Memory

- IR -- Instruction Register

- DE -- Instruction Decoder

- S1 -- Pipeline Registers of Stage 1

- S2 -- Pipeline Registers of Stage 2

- ALU -- Arithmetic Logical Unit

- R1 -- Register File ( Temporary )

- R2 -- Register File ( Submitted )

- MUX1 -- Multiplexer, Selected by S1

- MUX2 -- Multiplexer, Selected by S2

好像从 12 级开始,不知道是因为王恒才老师退休了,还是学生感觉 Verilog 太难了,体系结构实验改成了开发仿真器,主要工作从时序逻辑变成了图形界面 ^_^

- 课程难度:中等

- 作业多少:很少

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:很少

- 给分:超好

- 收获:很多

给周老师打一个满分!

首先说一说课程定位,这门课名字起的很大,实际上主要是传统arch研究领域大串烧(ISA, mem system, ILP, DLP, TLP),很遗憾没有来及说DSA相关的课程,因为这一章是现代arch研究热点和前沿,基本上都是10年内的方法(至少H&P书上包括了TPU,Nvidia GPU,Catapult等新兴架构介绍)。

周老师上课非常认真,会介绍很多技术细节,当然自己看ppt自学也可(非常详细!),都是很经典的方法。

作业很少基本没有(辅修人偷懒少做了一两次),实验主要是基于gem5的框架,把官网教程看懂问题不大。

最后考试和夏令营对对碰了,仗着辅修就没复习。听前面同学说比往年容易很多,至少我感觉上手难度不大,基本上都是见过或者基础的模型。

给分我感觉是超优秀率了,最后竟然上了4。很感谢周老师和助教老师一学期的教学。

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:很多

今年的期末题实在是太离谱了,拿起卷纸一道题都不会。。。 作业不是很多,实验可以有两种供选择,一种是祖传verilog,一种是新出的gem5,大概借鉴了部分UCLA的ca实验,整体难度适中,动手较少,理解性要求较高,报告要写的内容比较多。 老师的给分超神,不愧是周佛海,大慈大悲,考成那个德行还给我捞上来了

- 课程难度:中等

- 作业多少:中等

- 给分好坏:一般

- 收获大小:没有

- 难度:中等

- 作业:中等

- 给分:一般

- 收获:没有

?这评分巨离谱。前半段跟组原没差,都是一些小学奥数题。后半段零零碎碎讲了一大堆东西。总而言之没什么美感。ppt挺乱的,但是还是最后三天刷ppt学的。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:很多

体系结构这门课属于绝对的硬核课程,课程的难度不小,而且作为硬件课,是真的容易听不下去,上课听着听着就不知道在讲啥了,然后就再也听不懂了。

周老师讲课讲的非常不错,知识点什么的都非常清晰,课件跟着课堂内容一起看,完全没有问题,但是作为复习内容来参考的话,就会变得太冗杂了。因为其中补充了很多工业化的实现结果以及一堆图表数据(然而这些并不是知识点),穿插在各个知识点中间的话,复习的时候看起来就容易抓不到重点,容易陷入“我这里到底该不该看该不该记呢”这样的困惑。

本学期课程实验改革,助教们都非常认真负责,实验的设计以及相关文档,提供的基本程序都做的非常好。

实验有以下几个:

1. 设计RISC-V指令集下的流水线CPU

2. 根据设计用Verilog实现CPU并通过仿真测试

3. 给CPU加上Cache

4. 给CPU加上分支预测器

5. 根据提供的模拟器的运行结果完成实验报告,分别是Tomasulo,MSI,分布式MESI的

实验仓库链接:https://github.com/Summer-Summer/ComputerArchitectureLab

课程主页链接:http://home.ustc.edu.cn/~candrol/

往年都是有期中考试的,但本学期没有期中考试,只有期末考试,考试闭卷,该记的都得记。考了不少的计算,但大部分都没有过分为难,都很基本,唯独有一个向量处理器那章的chime,convoy相关的有些需要思考,题目基本上就是改编自课件例题,但这块要考虑的因素挺多的,老师也说题目提供的条件可能不全,所以在作答时,把你认为需要加上的条件加上(也就是说能自圆其说就好了233333【谁知道呢

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:很多

个人觉得周老师属于那种上课全程高能的老师,如果认真跟着老师听会觉得老师讲的很好,但是稍微一个走神就容易发现自己完全跟不上老师的节奏,接着就听的不明所以,所以大部分人选择了期末自己啃PPT。当然这也和硬件类课程本身非常枯燥无聊有关,老师某种意义上也已经尽力了……(拥有这种属性的老师还有:xyl、昱姐,etc)

体验不算好的一点是:PPT完全为上课服务,上课记笔记的体验非常好。老师对PPT中的内容也非常熟悉,可以看出经过了充分的备课,但是到了复习的时候,上课讲的案例和具体课程知识内容常常混杂在一起分不清,而且部分教学内容在配套教材上找不到。老师后半学期也在注意改善这个问题,但是前半学期的PPT已经改不过来了……

上课有几次点名,都是弱智级的题目,去了就是满分,而且今年开了两个班,所以可以互相充当僚机23333。

往年是有期中的,今年由于开了两个班不太好安排,因此直接将期中缩水为了小测,让你写对课程、实验的意见2333。老师在下一次的课上就针对了所有提出的问题一一做出了回答,感觉科大CS能做到这一点的老师还挺少的,在这里给老师点个赞。

期末考试题量比较大,而且有些题目比较怪(关于cache的一道题目,我没理顺其中的内在逻辑,花了好多时间),总体来讲中规中矩,还有一道5分的送分题(让你写对课程、实验的意见2.0,23333)

实验应该是这学期课程改革的一大亮点了,根据老师自己的描述,往年都是写tomasulo模拟器、cache一致性模拟器,闹到最后就是在写图形界面,被人诟病说:“硬件实验不够硬”,因此今年采取了大刀阔斧的改革,准备向UCB的对应课程看齐,重新启用了vivado&verilog,弄得一片鬼哭狼嚎

实验主要分为流水线设计文档、流水线(RISC-V版)、cache、分支预测、tomasulo模拟器分析等几个部分,根据助教的描述,下一年的实验还会继(jia)续(da)改(nan)革(du),今年的实验内容更多程度上是一个试水(这一点可以从占了大半学期,并且和COD高度重合的流水线、只是一个不算难的代码填空的cache中看出),所以……hhhhh

给分可能是两个班一起给的(保证公平性)

个人觉得自己学这门课学的比较认真,但是最后的分数不温不火,可能是考试的时候出的问题比较多,需要反思。

另外,老师上课上到后半学期嗓子都哑了,心疼老师。

还有,这学期助教真的都非常负责,实验文档写的相当完善,实验指导也非常详细,大大降低了实验难度。点名表扬.jpg

- 课程难度:中等

- 作业多少:很少

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:很少

- 给分:超好

- 收获:很多

现在是2025年6月15日晚上23点

明天上午八点半考试

由于考前各种事情堆杂在一起,导致并没有很系统的复习(dbq)

平时分,作业,实验基本上应该是满的

算了下考试只占35%的话估计考四十几分就能有3了(完全按照比例算的情况下)

并且我抱有期望老师可以捞捞

稍微刷了pksq往年的分享卷,大致学了下上面的内容

唉唉,PPT是英文掺杂的,课是会去上但是没听过的,作业题参考题是少的可怜的

希望考的都是看过的吧,不要考太偏或者考太多没看过的()

先给个10分期待老师捞捞

出完成绩再更,相信周佛海老师

直接出了总评,84卡绩了。

今年选课的是15个人,不知道优秀率给满没。

虽然卡绩没上优秀有点难受,但是想到自己考前疯狂预习,这个结果完全可接受。

考试考了几道小测题原题,一般上课小测老师会给我们讲完再收,所以可以在讲解的部分好好听一下。

其他的和PPT上的例题比较类似吧,题型和考察的知识点大致一致。

考了MIPS、FLOPS计算,各种指标的计算,吞吐量之类的。

考了分支预测的小测题,考了指令流动态调度方法(好像考的是Tomasulo,笑死考前简单过了一遍没想到考试真让我手搓全过程)

后面的记不清了,总之有一些偏文字定义的东西有印象就行,简答只有最后的一点,前面大部分还是计算和算法。

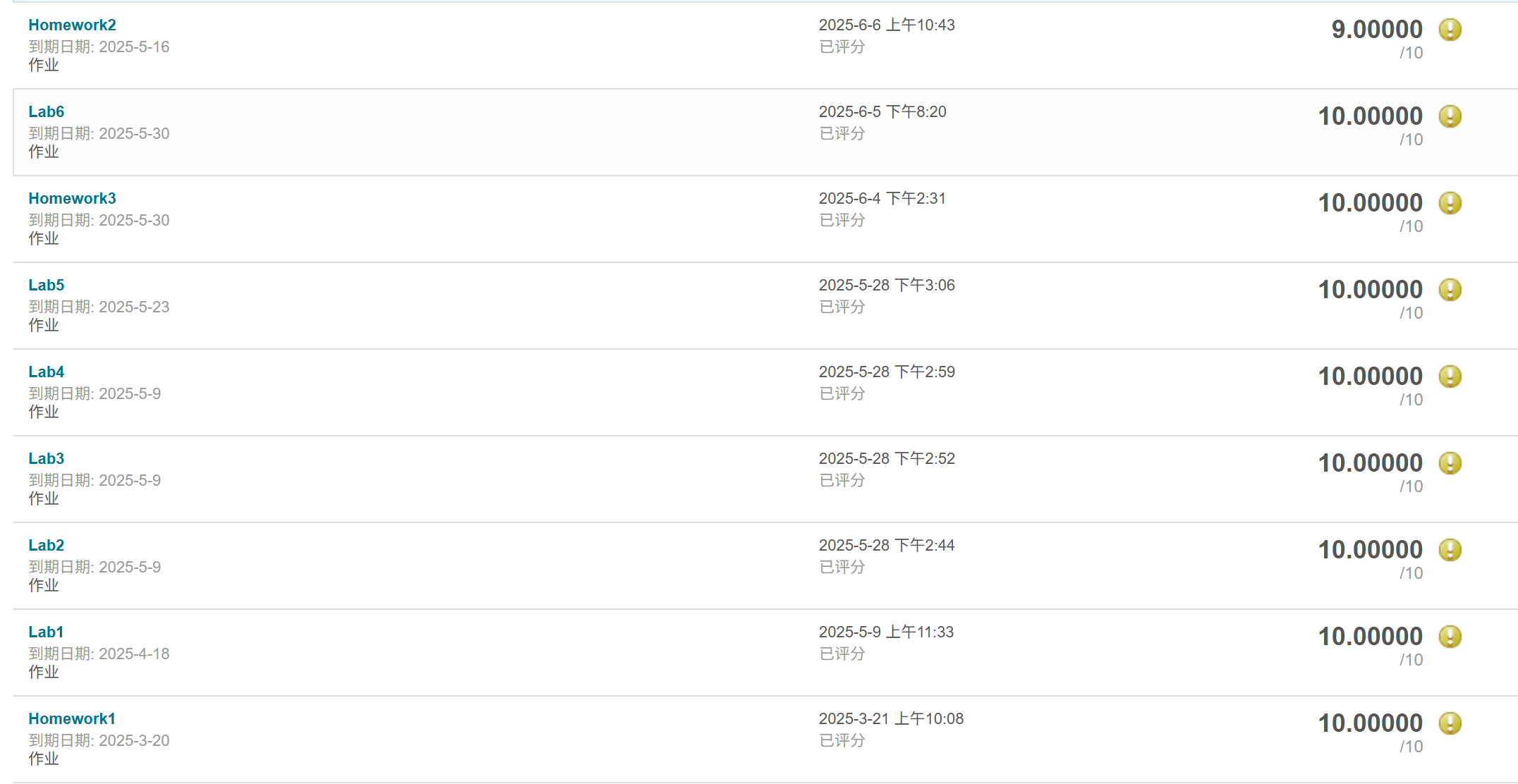

放上作业和实验的全部评分

总体上作业实验花费的时间不多,比一些其他选修课还是要轻松一点点,除了期末闭卷考试之外。。。

资料有空了会上传到github。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:一般

- 收获:一般

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:很多

今年考试特别难,每道题都不太确定,感觉可能最后只有个四五十分,总评奶到了优秀以上,我佛慈悲!!

上课:

课程内容感觉已经多年未变了,都是从COD的基本内容开始,之后主要的内容包括Cache、指令流调度、向量机、GPU、线程并行等。课堂讲课比较枯燥的,基本上都靠BB回放1.5倍速异步学习。平时上课人很少,但是如果前一节课通知小测,则教室基本坐满(老师也很懂)。

作业:

作业基本上是祖传的,可以在往年学长的Github上找到参考答案。有的作业题目意义非常不明或是少给条件,很离谱。

实验:

今年实验与以往不同,增加了gem5赛道,既可以选择Verilog也可以选择gem。gem实验部分似乎参考的是UCLA的CS251A,个人感觉Gem实验的报告量特别大,很多时候实验报告能写一晚上)。当然gem5网上能参考的资料比较有限,所以基本上靠自己根据自己的理解来回答来编。但事实上做完收获还是不少的。

考试:

今年考试特别难,考点基本上与往年相同,靠着录播和往年卷速成了几天。最后没有公布期末考的成绩,直接给总评,按反响来看还是比较奶的。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:一般

- 收获:一般

这门课以后改选修了,也不知道教学内容会不会变化。大三下很多同学都在忙别的,对课内的课程重视程度大大降低。此处先就本学期的教学内容进行叙述:

老师:

好,被誉为周佛海

作业:

作业量适中,且可以找到答案。

上课:

没听过不表。会小测,但小测前一节课会通知。

实验:

前四个实验分verilog和gem两种选择。verilog是组原2.0,组原实验完成的好的同学可以轻松完成,不想再见到vivado的同学可能有些困难...不过不需要上板;gem是今年新加的,具体不清楚,可能比verilog工作量小些(存疑),不过有安装需要很多内存和资料少的问题。

第五个实验是矩阵乘法的各种优化,包括向量化和CUDA等。这个实验应该挪到隔壁并行去......今年第一次有,出的问题似乎比较多,比如服务器申请不到啥的,文档也非常不详细,不过CUDA配置熟练的同学可以忽略这个。

第六个实验送分。

考试:

今年状况极为惨烈,就没几道题能够看懂...本身体系结构的内容就很多,这次卷子出的实在是太惨烈了。当然,我认为有很多地方表述确实存在问题。

给分:

考试虽然看不懂且难,不过优秀率应该给满了。

总结:

体系结构和系统等方向同学必上,其它方向同学可以综合考虑。

- 课程难度:困难

- 作业多少:很少

- 给分好坏:一般

- 收获大小:很多

- 难度:困难

- 作业:很少

- 给分:一般

- 收获:很多

感觉是这学期内容最多的课,考前一天看ppt还看不完。

数电-计组-体系结构,体系结构的实验反而是最容易的(或许与对verilog熟悉了有关?):前两个实验相当于计组扩展一点点,第3个是cache第4个是分支预测,56都不用verilog,比较好水。

作业的题都是最主要的知识,相反考试会考一些次要的内容,所以还是有必要认真上课的。

老师上课有点催眠,有小测,小测前一节课会通知,就导致平常教室只有1/3的人,小测当天教室会坐满。老师也感叹“我不搞小测你们就不来”,看上去怪可怜的哈哈。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:很多

给分真的很好了,本人自认为期末考炸,参考往年试卷一根筋去弄懂的chime没考,考了一大堆Tomasulo。但是总评却异常的好。

老师上课认真听其实是能学懂很多东西的,可是硬件课属实硬,上课稍微走个神就跟不上了,这是个人的问题。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:一般

课程定位:计组续集;一门需要通过占比较大的小测来勉强维持人数的课;学院极力打造的特色课;反正你也逃不掉(

课件:差不多就是李曦的ppt再加上中科大背景,垃圾的要死。别指望考前自己看能学到什么东西

实验:和往年重复度很高。lab1只有报告;lab2写cpu;lab3写cache;lab4写分支预测;lab5玩玩一致性模拟器。lab3和lab4的实验报告占比比较大,需要用编写的程序对给定问题进行测试、分析

考试:今年画风改了,考了一堆tomasulo和记分牌。考前在网上查各种资料,好不容易把向量处理机弄明白了,结果一分也没出

给分极好。我考完下来算算卷面40左右?最后给奶到84了(对于我这种学了体系结构连tomasulo都不会的人,已经知足了)...

老师第一个课件里就让大家思考这门课与计组的区别,然而我一直到了期末突击时才有了点体会

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:一般

周学海老师给分真的好,平时分占比很重,小测 实验 作业一定要认真完成,我平时分基本拿满了,期末在做的不是很好的情况下也拿到了理想的总评

期末考试考了50分的记分牌和tomasulo算法,托马斯洛算法占大比例

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:很多

从2019年开始,本课程的实验发生了改变,改成了用Vivado写Verilog实现RV32I流水线CPU、实现Cache、分支预测等。所以为了这门课还要把几十个G的Vivado装回去...实验内容看着比较多。由于Verilog的debug不太友好,难度主要在思路上。所以要一开始就要把思路捋明白。

课程PPT比较概括,适合做上课的提纲,但有一些错误,且对复习不太友好。每次上课前会更新PPT,所以要确保你下载的PPT是新的。

考前可以给老师发邮件,直接找老师答疑。老师的办公室的位置:从西活观光电梯的那个门进去,直走右转,找到嵌入式系统实验室即可。西区网络中心已经搬走了,所以课程主页上给的地址信息不完全准确。

期末考题略难,给分还算较好。

- 课程难度:中等

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

- 难度:中等

- 作业:中等

- 给分:超好

- 收获:一般

考试之后觉得自己铁定炸了,不过分数出来后竟然还行ʘᴗʘ。总之给分应该是待你不薄滴

本课程的实验感觉还是印象深刻,手写流水线,cache替换,分支预测,也不难但要花一点时间。最后的tomasolo模拟还是很有用的。看文字永远也看不懂的tomasulo模拟一下就很清楚了

- 课程难度:简单

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:简单

- 作业:中等

- 给分:一般

- 收获:一般

一门不感兴趣、一开始就没准备认真学的课。老师讲课很好,偶尔听一听就有不少收获,小测会提前通知,实验和作业有参考的话其实写起来不太难。

关于给分,似乎周围只有我不觉得很奶。平时分几乎满,期末甚至自我感觉考得不错(助教表示无查卷环节),总评3.0

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:一般

老师讲得很好,听课收获很大,但是很容易跟不上节奏(每节课内容都很多,节奏很快)

扣了两分,是因为课程本身的设置。这个课……对我而言真的好难……实验也不怎么会写…………期末卷子看不懂……悲

平时分占比很大,建议学弟学妹们平时分拉满,实验作业都好好写。每章的小测一定要去,占比不小。

(学的不好但是尽力了,最后低分飘过,感谢老师!)

- 课程难度:困难

- 作业多少:中等

- 给分好坏:超好

- 收获大小:一般

- 难度:困难

- 作业:中等

- 给分:超好

- 收获:一般

作业不算多,助教人超级好,周老师也超好,小测前一节课通知,实验是verilog和gem5二选一,gem5是新开的我没选,verilog万岁!主要形式是代码填空,框架助教给了,考试比作业小测难好多,但是期末占比不高,作业实验认真写就不错。

- 课程难度:简单

- 作业多少:很少

- 给分好坏:超好

- 收获大小:一般

- 难度:简单

- 作业:很少

- 给分:超好

- 收获:一般

为数不多的硬件课了,zxh讲的也还行,不过我听不下去。期末考试看PPT复习完事儿,没啥好说的。