2026春 2025春 2024春 2023春 2022春 课程号:21900401

- 课程难度:困难

- 作业多少:中等

- 给分好坏:一般

- 收获大小:很多

| 选课类别:计划内与自由选修 | 教学类型:实验课 |

| 课程类别:本科计划内课程 | 开课单位:微电子学院 |

| 课程层次:专业核心 | 学分:2.0 |

课程内容

《微电子专业基础实验》课程主要包括器件实验、模集实验和数字实验,每部分由不同老师负责。在器件实验中,学生进行软件仿真及实际测量,而模集实验和数字实验则主要通过仿真和代码实现。课程的难点在于数字实验,特别是大作业,要求一定的Verilog和Testbench背景知识,许多学生在没有系统教学的支持下,自学中遇到了困难。实验设置较丰富,涉及仿真、报告撰写等,但整体负担较重,需要付出超过2学分的时间和精力。

考试与作业

本课程没有传统形式的考试,评估主要依据平时实验表现和大作业完成情况。大作业对最终成绩的影响较大,有学生指出:“平时的实验大家都去了,报告思考题都交了,对错区别也不会太大,大作业的完成情况基本就决定了你最后总评能不能拿到优秀。”

教学设施与材料

实验指导讲义详尽,并附有操作说明,学生按部就班很快能够上手。然而机房设施老化,经常影响实验体验;有学生反映电脑“开机四十分钟”等现象突出。

教学水平

各位老师和助教态度积极,尤其是在回答问题和提供解决方案方面表现优秀。同时,实验内容丰富,对于加深理解微电子领域的理论和实现能力帮助较大,尽管部分学生对课程的系统性教学安排和硬件环境持批评态度。

总体评价与建议

总体而言,课程挑战性较强,收获较大,尤以大作业为关键评估点。建议选课同学提前掌握Verilog等编程语言基础,以应对课程中的各种挑战。希望课程能改进系统性教学与设备条件,进一步优化学生的学习体验。

- 课程难度:困难

- 作业多少:中等

- 给分好坏:一般

- 收获大小:很多

- 难度:困难

- 作业:中等

- 给分:一般

- 收获:很多

最由衷的建议就是23系看见这条评论的学弟学妹们寒假抓紧把Verilog和Testbench给提前学了,不然数字实验大作业你能卡在第一步代码仿真那儿怀疑人生。

实验从第六周开始,第十五周结束(真正啥时候结束取决于你后面模集实验大作业和数字实验大作业做的快不快,早做完早结束)。主要分为三个部分:器件实验、模集实验和数字实验。器件3次,模集6次,数字4次(三个部分各有一位老师负责,几乎都是机房上机软件仿真,除了大作业交报告平时每次都只要交实验讲义后面的思考题);中间有一次周六去微纳加工中心学习参观(挺有意义的,就是站俩小时有点累),还有五次华大九天实验(占用一定课时自行跟着PPT完成,助教不检查实验,只交思考题)。

今年做的比较好的是基本每次实验都有实验指导讲义,写的也都比较明白,上机跟着讲义做就行了,基本没太多问题(当然内容确实不少)。不用担心平时无脑跟做会不会没有收获,一个大作业逼着你翻讲义做完你就什么都会了(狗头)。

器件实验比较轻松,前两次在机房软件仿真,最后一次去实验室用SM-4 多探针电学测量平台测肖特基二极管的I-V特性曲线(助教指导一下就会,很快),没有特别的大作业。

数字实验前面四次每次花时间都不短,而且经常会有一些稀奇古怪的硬件问题(如机房电脑开机四十分钟等等);最要吐槽的就是四次实验之后的大作业。我觉得这门课让我体验最糟糕的就是完全没安排相关课程系统学习的情况下(感觉也没怎么提前预告),让我用Verilog来写大作业。在此之前我就寒假看到数集群里发的学习链接自己随便做了做,知道了一些简单语法仅此而已(懂语法跟用它来实现代码仿真真就完全两码事)——大作业一下来,被迫学期中一边上课,一边速成verilog和testbench强行上手(本身这学期个人算上一门重修就有七门专业课两门实验课要搞,真的罩不住)。最后花了好长时间,在好兄弟的帮助下,硬是让我那瘸腿代码跑成了。

想自学verilog的同学可以看看我们助教后来在群里发的菜鸟教程学习链接入门:https://www.runoob.com/w3cnote/verilog-tutorial.html

有足够多时间想更深层次学习的可以看看这本书(不知道咋样,还没来得及好好看)

之前我还不相信这课真能让我考试周赶大作业,现在被迫信了。大三下期末开始的早,大作业的ddl设在计算机原理与嵌入式系统期末考完的第二天晚上,于是就有了考完试第二天清晨端着电脑跑到三教一屁股坐到晚上十一点关门疯赶ddl的我(呜呜呜)。要感谢助教,如果不是助教在ddl前给我耐心解答,我可能代码仿真完就准备放弃了(当然我属于比较菜的,大佬们早在考试周前就做完了)。但该说不说数字大作业真就是最后实验成绩的一个大分水岭,毕竟平时的实验大家都去了,报告思考题都交了,对错区别也不会太大,大作业的完成情况基本就决定了你最后总评能不能拿到优秀。

模集实验最大的特点就是自从看过模集讲义,再长的实验讲义都唬不住我了——实验讲义内容特别多,每次三十多页到五十多页不等,而且仅仅是一下午/一晚上的量。不过该说不说,内容多,讲的确实清楚,不少内容还是老师自己补充的,看看就行了。每次实验虽然时间有点紧俏,而且有时会戴上痛苦面具,但基本都能做完。第五次和第六次实验合为大作业,不过都有讲义;据说以前只给放大器版图和参数要求,要你根据这些要求自己画版图设参数仿真来满足;今年比较银性,给了比较详细的操作指导,总体来说难度并不大,就是内容真的多。最大的建议就是中间每一步务必跟着实验报告做并截图,别跳步,做完直接写报告,等做完再回过来截真的心态都截炸了。 总的来说模集实验还是不错的,学会了很多东西,室友也在说模集实验是他这学期收获最大的实验。

这门实验课算是23系专业核心课程之一,需要你花费的时间精力远超2学分,但老师助教都很好,实验讲义写的也很详细;学院老师们也一直在想方设法改进实验,总的来说收获确实是很大的(这可能也是实验课的特点吧)。真心希望verilog的问题能在下一届解决了,毕竟现在回想起自己数字大作业的历程都心有余悸(捂脸)。祝愿这门课越开越好吧。

最后总评给了4,咱也不知道分具体是怎么算的,不过个人觉得也算对得起自己在这门课上的付出了。

- 课程难度:困难

- 作业多少:中等

- 给分好坏:一般

- 收获大小:一般

- 难度:困难

- 作业:中等

- 给分:一般

- 收获:一般

数字的大实验没写,模拟的大实验不知道写对没,喜提2.7,不过确实也没啥好讲的,想拿正常的分肯定还是要一些投入的

- 课程难度:困难

- 作业多少:很多

- 给分好坏:一般

- 收获大小:一般

- 难度:困难

- 作业:很多

- 给分:一般

- 收获:一般

内容多到想吐。

后面的模拟电路部分,40多页的PDF,电脑前一坐就是一下午+一晚上,要是遇到抽象bug,等死吧。

给分,很想吐槽,所🈶选修内容做了,大作业也认真搞了,喜提3.0。

收获只能说有,但是不多,照着PDF指导确实能做点看起来像东西的东西,但是其实自己还是啥都不会。

- 课程难度:困难

- 作业多少:很少

- 给分好坏:一般

- 收获大小:很多

- 难度:困难

- 作业:很少

- 给分:一般

- 收获:很多

数字部分:目前来看是两极分化的课程,让人觉得是不是少了系统性教学candence的一门课程,听说往届还没上过verilog课,更加难以评价。数字实验01到04基本是傻瓜式的实验文案,恨不得手把手指挥你干事但是又不说为什么;大作业部分好比高中电磁学完直接和电磁场与波进行殊死搏斗,verilog、linux、incisive等等到处都是未解之谜。甚至物理设计部分还能出现神秘祖传器件bug,我只能说manba out

除此之外最逆天的是学校的机器和服务器。哦我的天,原来是xxx.xx.xx.xxx大人,速度快的、有响应的、即时交互的、打字不会在我输入完之后一个一个慢慢显示的、不会突然卡死推倒重来的、不会上个洗手间回来发现被踢下线又要重开的(绝对不是我因为这些问题重开了六遍实验三)。

再来就是大作业实验三部分的利用率记得要调低一点(我记得是一个0.7的数),最好调整到0.6 0.5比较保险。利用率太高会导致程序没法自动优化时序问题(太挤了加不了buffer,手动加了框框报错)。还有最最坑人的是实验三里2.15节是填充filler,3.x节才开始调整时序,但是filler填充之后也没空间加buffer了只能重开,我的建议是不如填充一下费勒斯(一定要先优化时序再填充filler!)

哦还有实验二检查一致性有些人可能不会通过,原因是一些输出可能包含在多个always里面导致有冲突,写代码的时候记得不要在多个always里分别写几个情况的输出。比如always(@*)ifxxx n<=1;always(@*)ifyyy n<=2这样写。

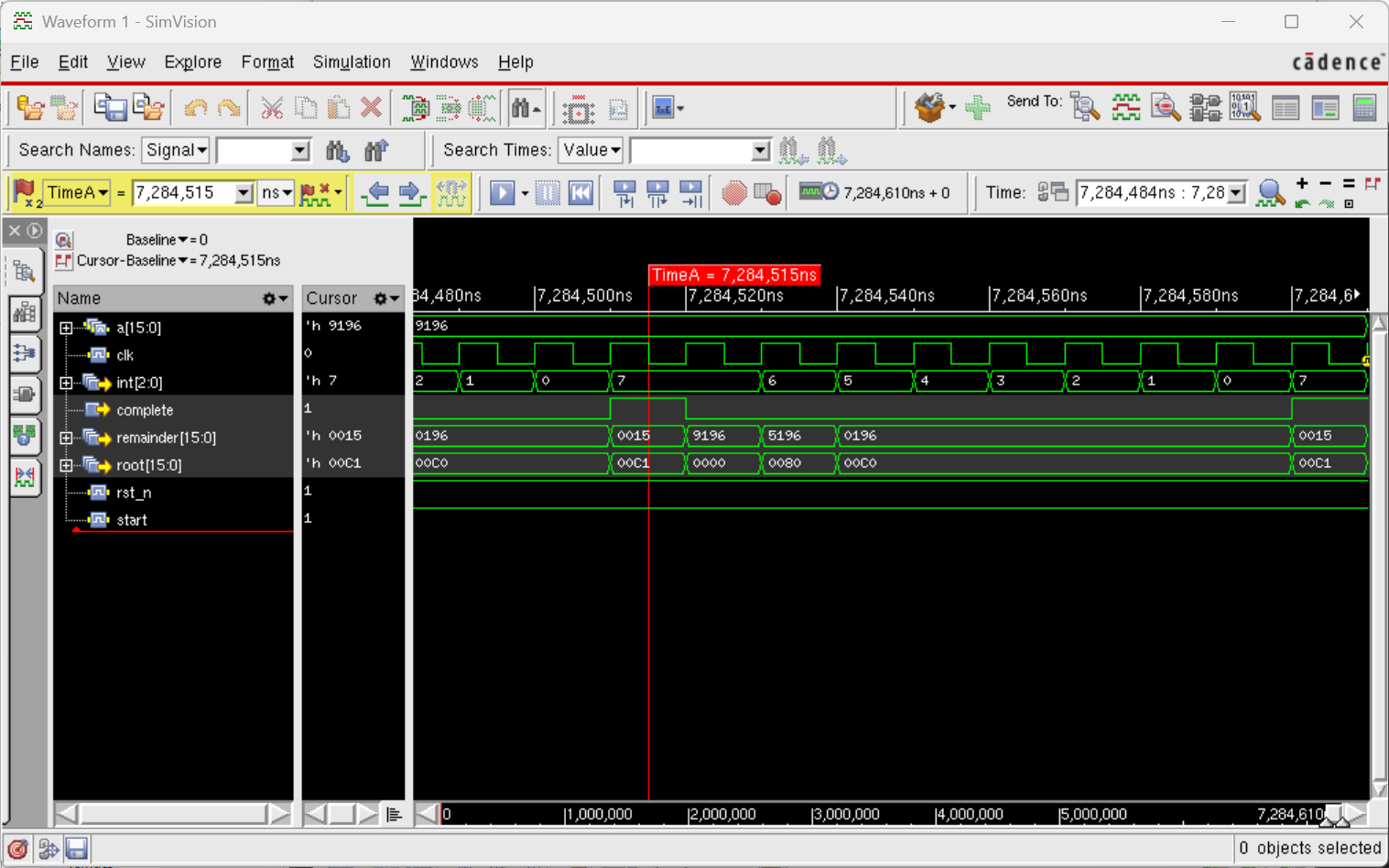

大作业这个代码真有点神奇了,算几百内的平方根都没问题,算上万的就一动不动了,明明位宽都是够的,这程序本质算再多位也只是超模肥肉的堆砌,怎么会出问题呢?(这个问题算是解决了,PPT上给的输入位宽2N,平方根位宽N,余数位宽N+1;但是这个余数的位宽我估计是不够的,如果q7==0那余数就可能有2N-2位。所以我把输入、平方根和余数的位宽全部改成16位就可以算三四万都没问题了。)

用爆改之后的代码跑了一遍实验二,syn_opt直接干出来两个error,不过逻辑网表和Verilog代码的一致性检查还是PASS了。据说是工艺文件缺少的原因,不过优化部分报的错我也懒得管了,继续做实验三物理设计吧。

实验三做完了,物理验证和时序都一遍过,优化一下就没问题了。但是实验报告里还要求写电路网表仿真结果,我翻了实验三实验四的实验文档都没有相关的操作教学,这又是一个未解之谜了。(哦布莱克斯,原来这玩意在实验一的内容里,藏的确实好👍白雪飞老师态度非常好,指出问题和给的建议都简明有用,白神!不过网表仿真还是有问题,算了明天再看吧😰)

太无敌了,实验四用的innovus不是stylus模式,而我load我的golbal文件进去之后直接给我报错。用stylus模式生成netlist文件还是在file-save-netlist那里;而导出SDF文件就用write_sdf delays.sdf在命令行输入就好了。我把这两个玩意儿复制到simulation文件夹里再用incisive仿真一遍网表文件,给我报了2000+警告,最后结果也不成功,彻底不明白是什么问题了。。